STM32时钟源(HSI/HSE/LSI/LSE/PLL)

- HSI 是高速内部时钟,RC振荡器,频率为8MHz;

- HSE 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz

- LSI 是低速内部时钟,RC振荡器,频率为40kHz;

- LSE 是低速外部时钟,接频率为32.768kHz的石英晶体;

- PLL 为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

注意:

其中40kHz的LSI(低速内部时钟)供独立看门狗IWDG使用,另外它还可以被选择为实时时钟RTC的时钟源。另外,实时时钟RTC的时钟源还可以选择LSE(低速外部时钟),或者是HSE(高速外部时钟)的128分频。RTC的时钟源通过RTCSEL[1:0]来选择。

SYSCLK时钟

SYSCLK系统时钟最大频率为72MHz,它是供STM32中绝大部分部件工作的时钟源;

- 送给AHB总线、内核、内存和DMA使用的HCLK时钟;

- 分频后送给STM32芯片的系统定时器时钟(

Systick=Sysclk/8=9Mhz),直接调用void sysTickTimerInit ( void )选择时钟源SysTick_CLKSourceConfig ( SysTick_CLKSource_HCLK_Div8 )即可使能; - 直接送给Cortex的自由运行时钟(free running clock)FCLK。【注:FCLK 为处理器的自由振荡的处理器时钟,用来采样中断和为调试模块计时。在处理器休眠时,通过FCLK 保证可以采样到中断和跟踪休眠事件。 Cortex-M3内核的“自由运行时钟(free running clock)”FCLK。“自由”表现在它不来自系统时钟HCLK,因此在系统时钟停止时FCLK 也继续运行。FCLK和HCLK 互相同步。FCLK 是一个自由振荡的HCLK。FCLK 和HCLK 应该互相平衡,保证进入Cortex-M3 时的延迟相同。】;

- 送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给定时器(Timer)2、3、4倍频器使用。该倍频器可选择1或者2倍频,时钟输出供定时器2、3、4使用;

- 送给APB2分频器。APB2分频器可选择1、2、4、8、16分频, 其输出一路供APB2外设使用(PCLK2,最大频率72MHz),另一路送给定时器(Timer)1倍频器使用。该倍频器可选择1或者2倍频,时钟输出 供定时器1使用。另外,APB2分频器还有一路输出供ADC分频器使用,分频后送给ADC模块使用。ADC分频器可选择为2、4、6、8分频;

备注:

- FCLK为供给CPU内核的时钟信号,我们所说的cpu主频为XXXXMHz,就是指的这个时钟信号,相应的,1/Fclk即为cpu时钟周期

- HCLK为优秀的高性能总线(AHB bus peripherals)供给时钟信号(AHB为advanced high-performance bus);HCLK :AHB总线时钟,由系统时钟SYSCLK 分频得到,一般不分频,等于系统时钟,HCLK是高速外设时钟,是给外部设备的,比如内存,flash。

- PCLK为优秀的高性能外设总线(APB bus peripherals)供给时钟信号(其中APB为advanced peripherals bus);

总线—APB和AHB

- APB Advanced Peripheral Bus的缩写,这是一种外围总线;

APB1总线外设

- 定时器TIM2到TIM7;

- RTC;

- WDT看门狗;

- SPI2 、SPI3;

- USART2、USART3;

- UART4、UART5;

- I2C1,I2C2;

- USB./CAN共享的512字节SRAM;

- bXCAN1、bXCAN2;

- 后备寄存器BKP;

- 电源控制PWR;

- DAC

APB2总线外设

- USART1;

- 高级控制定时器TIM1和TIM8;

- 模数转换器ADC1、ADC2、ADC3;

- SPI1;

- 外部中断EXTI;

- 复用IO,AFIO;

- 通用IO:GPIOA~G;

AHB外设

AHB Advanced High performance Bus的缩写,译作高级高性能总线,这是一种“系统总线”。

Flash 存储器;

DMA;

复位和时钟控制;

CRC;

以太网;

SDIO;

串口

- USART1 串口模式

| 模式 | 说明 |

|---|---|

| Sigle Wire(Half-Duplex) | 半双工 |

| Asynchronous | 异步 |

| synchronous | 同步 |

| SmartCard | 智能卡 |

| lrDA | 红外线数据协会) SIR ENDEC 规范 |

| LIN | 支持局域互连网络 |

| Multiprocessor Communication | 多机串口通信 |

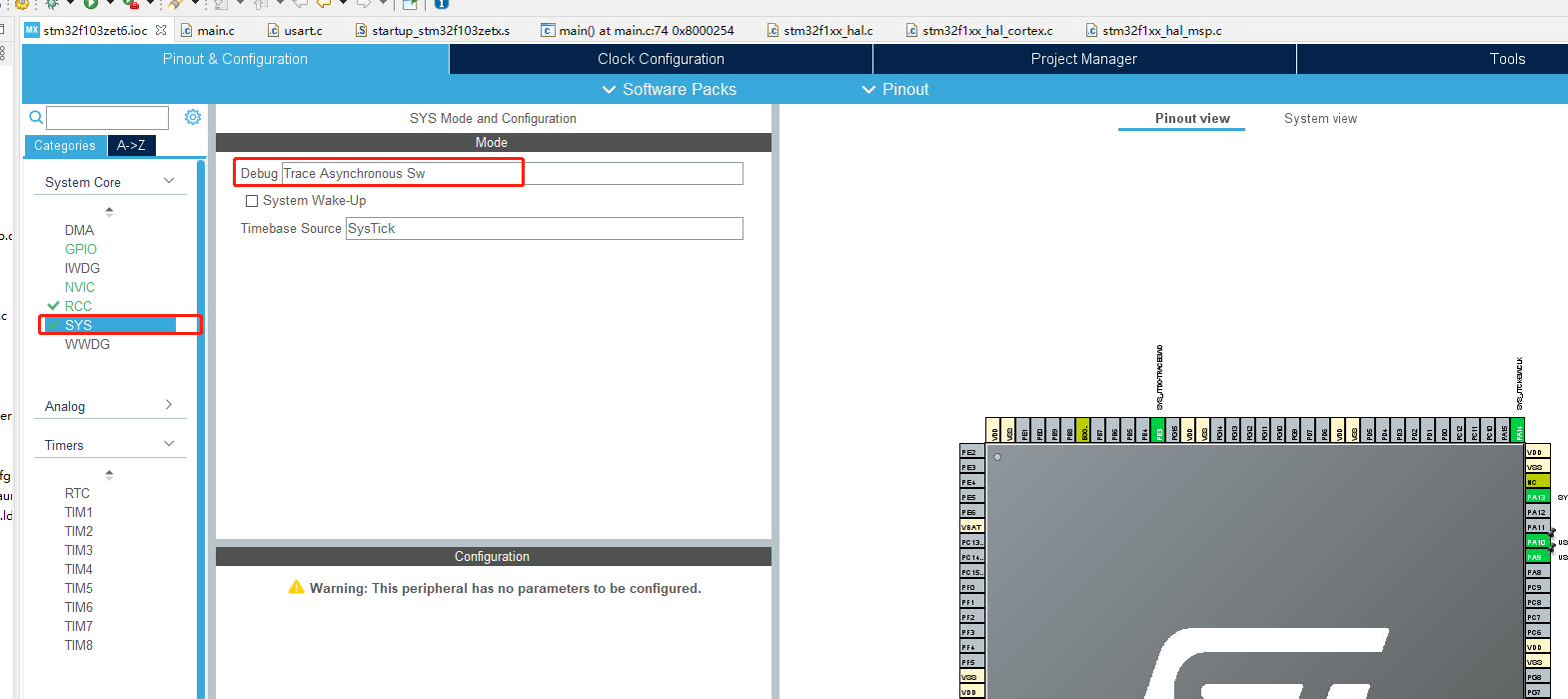

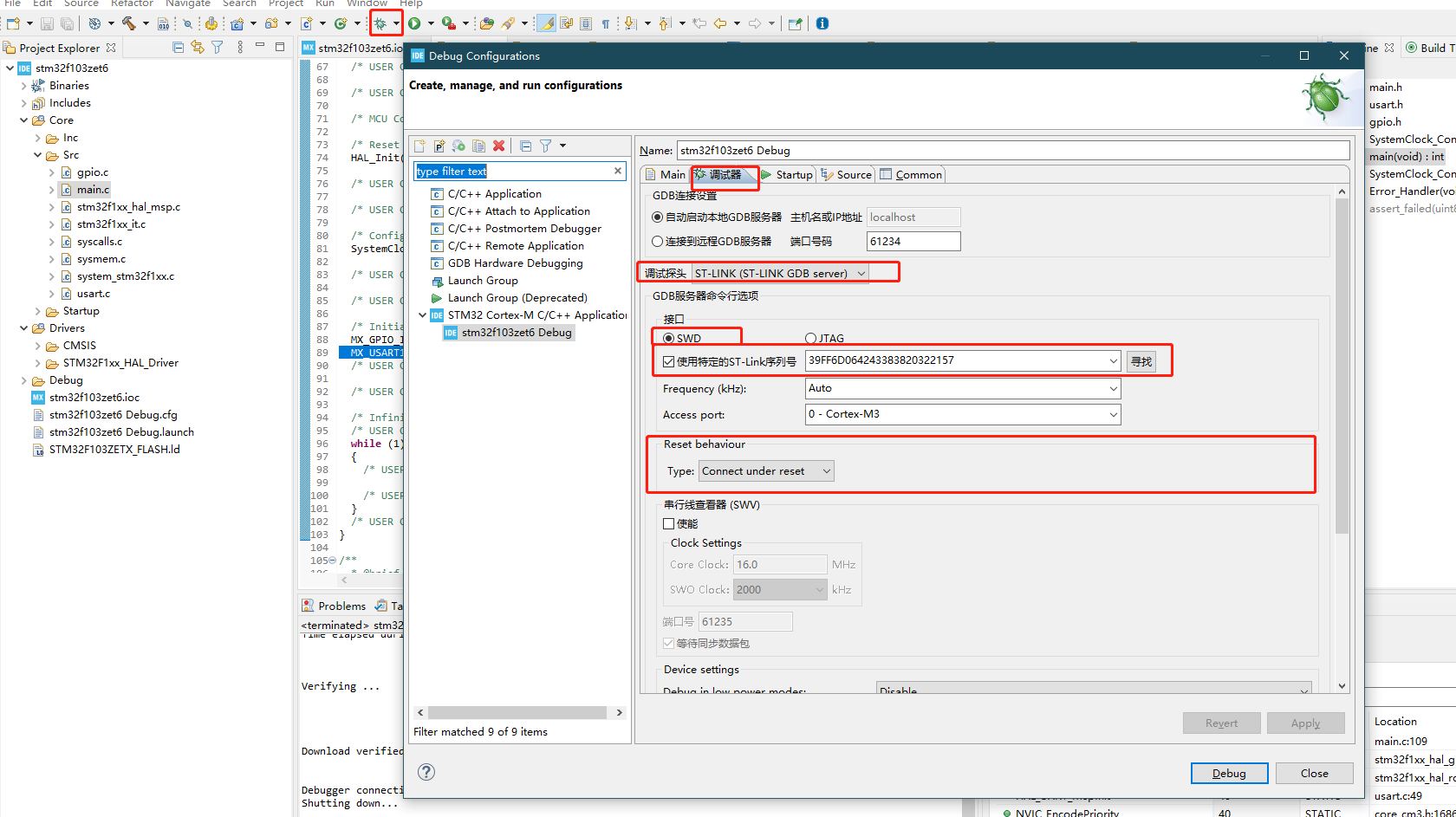

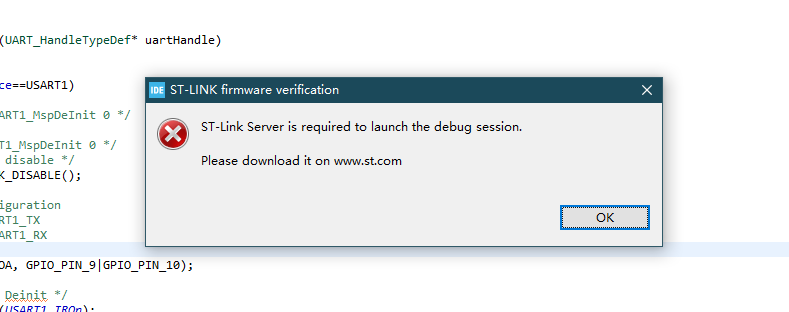

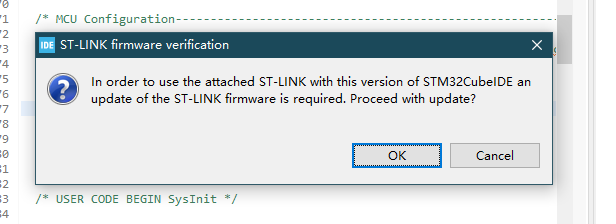

CubeIDE Debug设置

- 设置调试器(这里以ST-LINK为例子)

- 出现以下提示,需要下载对应的ST-Link Server

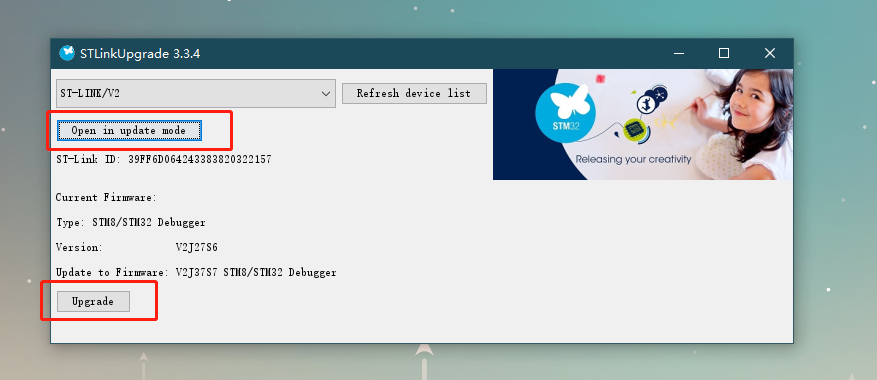

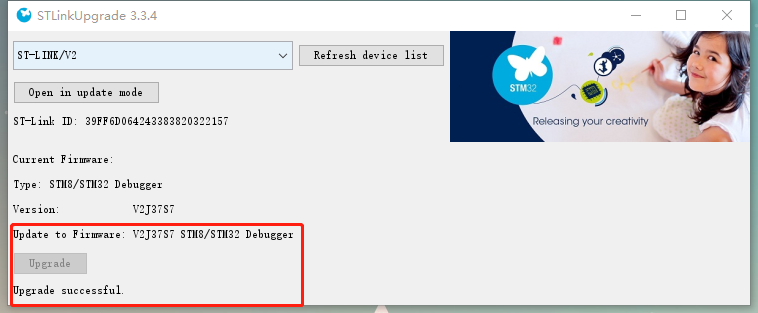

- 升级ST-Link 固件

- 设置SW 调试引脚,不然不能在线调试(这个细节我被坑了┭┮﹏┭┮)